Phone: +86-755-2357-1819 Mobile: +86-185-7640-5228 Email: sales@ominipcba.com whatsapp: +8618576405228

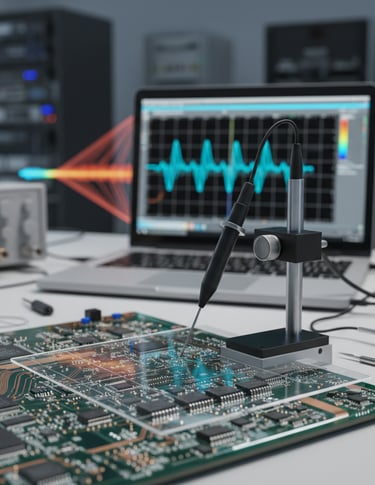

Signal Integrity: The Physical Reality Behind PCB Simulation

Bridge the gap between virtual simulation and physical reality. Master impedance control, minimize crosstalk, and validate high-speed designs before fabrication begins.

PCB TECHNOLOGYPCB MANUFACTURINGPCB ASSEMBLY

OminiPCBA

1/5/20267 min read

In the domain of modern electronics, the printed circuit board has transcended its traditional role as a mere connectivity platform. As edge rates accelerate into the picosecond range and data protocols push beyond 56 Gbps PAM4, the PCB trace transforms from a simple copper wire into a complex transmission line. Signal Integrity (SI) is no longer a niche discipline reserved for supercomputer backplanes; it is the fundamental constraint governing the success of everything from automotive radar modules to consumer IoT devices.

The shift is profound. At lower frequencies, electrons flow like water through a pipe, and resistance is the primary antagonist. In the high-speed regime, electromagnetic fields propagate through the dielectric material surrounding the conductor, and the copper merely guides the wave. This inversion of physics means that successful electronics production relies less on schematic logic and more on mastering the electromagnetic environment. Simulation is the lens through which engineers view this invisible world, but the correlation between the simulation deck and the physical board determines whether a product launches or fails.

The Transmission Line Environment

When the rise time of a digital signal is short enough that the signal has not finished transitioning at the source before the leading edge reaches the receiver, the interconnect behaves as a transmission line. This critical length threshold is shrinking. A trace as short as 10 millimeters can act as a transmission line in modern DDR5 memory interfaces.

The primary objective of SI simulation is to manage the characteristic impedance (Z0) of these lines. While Ohm’s Law governs DC circuits, the telegrapher’s equations govern transmission lines, dictating that impedance is a function of inductance and capacitance per unit length. Any deviation in the cross-sectional geometry of the trace—whether caused by a routing turn, a component pad, or a manufacturing variance—creates an impedance discontinuity.

When a travelling wave encounters a discontinuity, a portion of the energy is reflected back to the source. These reflections manifest as ringing, overshoot, and undershoot in the time domain, effectively closing the data eye. If the overshoot exceeds the voltage tolerance of the receiver's input buffer, it causes latch-up or permanent silicon damage. Conversely, undershoot erodes the noise margin, causing false switching.

The Return Path: The Hidden Half of the Circuit

A prevalent misconception in layout design is that signals travel from point A to point B. In reality, current always travels in a loop. For every signal launching down a trace, an equal and opposite return current must find its way back to the source. At DC, this current follows the path of least resistance. However, above a few kilohertz, the return current follows the path of least inductance, which is directly underneath the signal conductor.

This behavior allows for tight coupling between the signal and its reference plane, minimizing loop area and reducing Electromagnetic Interference (EMI). The simulation challenge arises when this return path is broken. A split in the ground plane, often introduced to isolate analog and digital sections, forces the return current to detour around the gap. This detour increases the loop inductance, creating a slot antenna that radiates noise and degrades the signal edge rate.

Advanced PCB assembly workflows increasingly rely on stitching capacitors to bridge these gaps, but simulation is required to verify that the capacitor’s parasitic inductance does not render it transparent at the operating frequency. Analyzing the return path density plots in 3D field solvers allows designers to visualize where the current is constricted, preventing EMI failures that would otherwise only be caught during compliance testing.

Impedance Control and the Fabrication Gap

Simulator tools assume ideal geometries: perfect rectangular traces and consistent dielectric constants. The manufacturing floor operates in a world of tolerances. The etching process is chemical; it eats away copper isotropically. A trace designed as a 5-mil rectangle ends up as a trapezoid, with the bottom width significantly larger than the top width.

This "etch factor" alters the calculated impedance. A design simulated at 50 ohms might physically measure 45 ohms if the trapezoidal effect is not accounted for. Industry benchmarks, such as those maintained by Ominipcba, demonstrate that collaborating on stack-up design before routing begins is critical. By inputting the fabricator’s specific etch compensation factors and press-out thickness values into the simulation tool, the virtual model aligns with the physical reality.

Furthermore, the dielectric height varies. Prepreg layers flow during the lamination press cycle, and their final thickness depends on the copper density of the adjacent layers. Areas with sparse copper allow more resin to flow away, thinning the dielectric and lowering impedance. Conversely, dense copper areas retain resin, increasing thickness. Post-layout simulation must account for these local variations to ensure the final board passes Time Domain Reflectometry (TDR) testing.

Crosstalk: The Enemy Within

As density increases, traces are pushed closer together, intensifying electromagnetic coupling. Crosstalk is the unintended transfer of energy from an aggressor line to a victim line. It manifests in two forms: Near-End Crosstalk (NEXT) and Far-End Crosstalk (FEXT).

NEXT is particularly damaging because it travels backward toward the source, potentially summing with reflections to destabilize the driver. FEXT travels along with the signal to the receiver, directly impacting the timing budget and voltage margins. The traditional rule of thumb—spacing traces at "3W" (three times the trace width)—is often insufficient for modern high-voltage swing signals or extremely sensitive analog lines.

Simulation allows for the analysis of coupling coefficients across the entire length of the bus. In strip-line configurations (traces sandwiched between two ground planes), FEXT can theoretically be eliminated if the dielectric environment is homogeneous. However, in microstrip configurations (outer layers), the difference in propagation velocity between the fields in the air and the fields in the dielectric ensures that FEXT is always present. Solutions involve utilizing "guard traces," though these must be stitched to ground frequently to avoid becoming resonant antennas themselves.

The Via Discontinuity Problem

In the context of multi-layer turnkey PCBA designs, signal transitions between layers are inevitable. The Plated Through Hole (via) is the most significant parasitic element in a high-speed channel. Electrically, a via is a complex structure exhibiting capacitive coupling to the reference planes and inductive properties along its barrel.

The most insidious aspect of a via is the "stub"—the unused portion of the barrel that extends beyond the signal layer to the bottom of the board. This stub acts as an open-ended transmission line. At a specific frequency, the stub length equals one-quarter of the wavelength, creating a resonance that shorts out the signal, resulting in a deep notch in the insertion loss plot (S21).

Backdrilling is the standard remediation in EMS manufacturing. By physically drilling out the unused copper stub, the resonance is pushed to a much higher frequency, outside the bandwidth of interest. Simulation dictates exactly how deep the backdrill must go and how much tolerance margin is required to avoid severing the internal connection.

Material Science: Glass Weave and Skew

At data rates exceeding 10 Gbps, the microscopic structure of the PCB laminate becomes a dominant variable. Standard FR-4 is a composite of woven glass fibers and epoxy resin. Glass has a Dielectric Constant (Dk) of approximately 6.0, while resin sits near 3.0.

If a differential pair is routed such that one leg travels over a glass bundle (high Dk) and the other over a resin-rich trough (low Dk), the signals will propagate at different speeds. This "fiber weave effect" introduces intra-pair skew, converting the differential signal into common-mode noise and collapsing the eye diagram.

Simulation tools can model this statistically, but the fix is often mechanical. Zig-zag routing or rotating the artwork by 10 degrees relative to the weave panel prevents any single trace from aligning perfectly with the glass bundles. High-end implementations reviewed by Ominipcba often utilize "spread glass" fabrics, where the glass fibers are mechanically flattened to close the gaps, providing a more homogeneous medium for the electromagnetic field.

Power Integrity (PI): The Foundation of SI

Signal Integrity cannot exist without Power Integrity. The voltage regulator module (VRM) may provide a clean 1.2V DC, but the high-speed switching of millions of transistors creates massive transient current demands. If the Power Distribution Network (PDN) has high impedance, these transients cause voltage ripple (rail collapse).

This ripple creates Simultaneous Switching Noise (SSN), which couples into the signal drivers, causing jitter. A driver starved of voltage cannot transition as fast, delaying the signal edge. Simulation of the PDN impedance profile—aiming for a "flat" impedance across the frequency spectrum—is essential. This involves placing decoupling capacitors as close to the active pins as possible.

The SMT process plays a role here. The mounting inductance of a capacitor is determined by its loop area, which includes the pads, the vias, and the distance to the plane. A poorly placed capacitor is electrically invisible to a high-frequency transient. Co-simulation of SI and PI allows designers to optimize capacitor placement and via fan-out patterns to minimize loop inductance.

S-Parameters: The Universal Language

Frequency domain analysis relies on Scattering Parameters (S-parameters). For a simple two-port network (like a single trace), S11 represents Return Loss (how much energy is reflected), and S21 represents Insertion Loss (how much energy gets through).

In high-speed design, the goal is to minimize S11 (ideally < -15dB) and optimize S21 to have a smooth roll-off without resonant dips. The simulation of S-parameters is critical for compliance with interface standards like USB4 or PCIe Gen 5. These standards specify strict limit lines (masks) that the channel must not violate.

However, simulation is only as good as the material models. Many generic material libraries fail to account for the variation of Dk and Df with frequency. Using wideband Debye or Djordjevic-Sarkar models provides a more accurate representation of dispersion, ensuring that the simulated phase delay matches the physical measurements taken by Vector Network Analyzers (VNA) post-assembly.

Jitter and The Eye Diagram

The culmination of all SI efforts is the Eye Diagram. This overlay of multiple bits allows engineers to visualize the signal quality at the receiver. The "opening" of the eye represents the noise margin and timing budget.

Jitter—the deviation of the signal edge from its ideal timing—is the primary mechanism that closes the eye horizontally. Simulation separates jitter into Random Jitter (RJ), which is unbounded and Gaussian, and Deterministic Jitter (DJ), which is bounded and predictable. Inter-Symbol Interference (ISI) is a form of DJ caused by the bandwidth limitations of the channel (loss).

Pre-emphasis at the transmitter and equalization (CTLE/DFE) at the receiver can open a closed eye. Modern simulators allow designers to model these active equalization circuits, tuning the tap weights of the equalizer to compensate for the specific insertion loss profile of the PCB trace.

Conclusion: Closing the Loop

The gap between a "pass" in simulation and a functional board on the bench is bridged by process knowledge. An impedance model is useless if the lamination press cycle is uncontrolled. A crosstalk analysis is invalid if the registration tolerance of the drill creates unintended coupling.

Signal Integrity is a circular discipline. It begins with theoretical physics, moves through computational modeling, and finds its validation in precision electronics production. The partnership with an experienced manufacturer, one who understands the RF implications of solder mask thickness and surface finish conductivity, is the final variable in the SI equation. By treating the PCB as an active component and validating every parasitic element through rigorous simulation, engineers can ensure that the digital heartbeat of their product remains strong, stable, and reliable.

Related Articles

Contacts

Email: sales@ominipcba.com

Mobile: +86-185-7640-5228

Copyright © 2007-2026. Omini Electronics Limited. All rights reserved.

Head Office: +86-755-2357-1819

Services

Your China turnkey partner for electronics manufacturing. We bridge design to delivery by leveraging the Shenzhen electronics ecosystem for precision engineering and streamlined PCBA supply chain logistics.

Ready to Build?

Get a comprehensive quote within 24 hours.